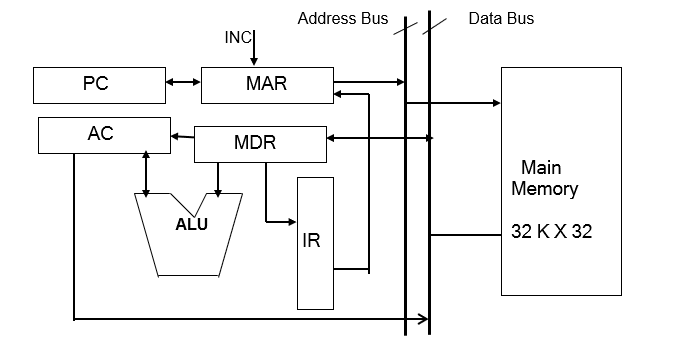

The hypothetical architecture with connection is shown below.Write fetch, decode and execute cycles for the BSAL instruction. This instruction is used for subroutine orprocedure. When executed, the BSA instruction stores the address ofthe next instruction in sequence into a memory location specifiedby the L. The effective address L plus one is then transferred toPC to serve as the address of the first instruction in thesubroutine. Use D5 – Decoder output for BSA instruction (not shownin this figure).